# CSDL: REUSABLE COMPUTING SYSTEM DESCRIPTIONS FOR RETARGETABLE SYSTEMS SOFTWARE

#### **A Dissertation**

Presented to

the Faculty of the School of Engineering and Applied Science at the

University of Virginia

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy (Computer Science)

by

Mark W. Bailey

#### APPROVAL SHEET

## This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Science)

| ssertat | ion has been read and approved by the Examining Co    |

|---------|-------------------------------------------------------|

|         | Dissertation Advisor (Jack Davidson)                  |

|         | Committee Chairman (Alfred Weaver)                    |

|         | James Cohoon                                          |

|         | John Knight                                           |

|         | Ronald Williams                                       |

| Accep   | ted for the School of Engineering and Applied Science |

May 2000

#### **ABSTRACT**

In an era of rapid design of microprocessors for desktop systems, embedded systems, and handheld computing devices, the timely construction of systems software is essential. Systems software, such as assemblers, compilers, and debuggers, must be constructed before development of application software for a microprocessor can commence. However, the implementation of such machine-specific applications is difficult and time consuming. Therefore, to remain competitive, it is imperative that systems software designs focus on portability to reduce implementation time and ensure rapid delivery of complete systems to the market. This dissertation presents the Computing System Description Language (CSDL) framework that addresses these rapid development requirements.

We illustrate the CSDL framework by developing an instruction-set description component ( $\tau RTL$ ), an optional procedure calling convention description component (CCL), and the mechanism we use to extend extant descriptions (CSDL).  $\tau RTL$  and its accompanying microinstruction descriptions ( $\mu RTL$ ) further the state-of-the-art in specifying semantics of machine instructions.  $\tau RTL$  adds a new type system and abstract syntax that facilitates more accurate specification and automatic detection of errors by  $\tau RTL$  manipulators.  $\tau RTL$  machine descriptions are also application independent—they completely separate the specification of semantics from the application's implementation. The CCL specification language is the first work to formally describe procedure calling conventions. We demonstrate two distinct uses for CCL descriptions: code generation and fault detection. Using CCL we have built compilers that are more robust, and found and diagnosed faults in production compilers. CCL,  $\tau RTL$ , and  $\mu RTL$  descriptions are bound together using CSDL. CSDL is the first description system to recognize that specifications must evolve and that specifications will frequently include application-dependent features. The CSDL environment provides facilities

| for adding new components, sharing information between components, and extending existing components for use in a wide variety of applications. |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

|                                                                                                                                                 |  |  |  |

#### **ACKNOWLEDGMENTS**

I would like to thank everyone who has contributed, supported, or encouraged me in this work.

First and foremost, I would like to thank my advisor, Jack Davidson. Over the many years, Jack has been much more than just an advisor; he's been a teacher and friend. I owe all of the good ideas in this dissertation to Jack. The bad ones are all mine.

The members of my examining committee, Jim Cohoon, Jack Davidson, John Knight, Alf Weaver, and Ron Williams had the unfortunate job of reading this dissertation cover-to-cover. I thank them for holding me to their high standards.

I could not have completed this degree without the wonderful support of the faculty, staff, and students in the Computer Science Department at the University of Virginia. There are, unfortunately, too many to list here. I've made so many friends and learned so much. In return, I will always be grateful.

All of my family supported me with encouragement and enthusiasm. In particular, my parents, Duane and Leeta, and my wife's parents, John and Carol provided much needed spiritual support. They never asked "how much longer?" at the wrong time.

Finally, I wish to thank my wife, Ann, for her love, continuous support and encouragement. I will never understand how she stuck with me during the hard times.

#### **CONTENTS**

| Chapter 1 | — Introduction                                             | 1  |  |  |

|-----------|------------------------------------------------------------|----|--|--|

| 1.1       | Background                                                 |    |  |  |

| 1.2       | The Problem                                                |    |  |  |

| 1.3       | Motivation                                                 | 5  |  |  |

| 1.4       | Structure                                                  | 6  |  |  |

| Chapter 2 | — Computing System Descriptions                            | 8  |  |  |

| 2.1       | Computer Hardware Description Languages                    | 8  |  |  |

|           | 2.1.1 VHDL                                                 | Ç  |  |  |

|           | 2.1.2 ISP                                                  | 11 |  |  |

|           | 2.1.3 Lisas                                                | 12 |  |  |

| 2.2       | Machine Descriptions                                       | 13 |  |  |

|           | 2.2.1 ISP´                                                 | 13 |  |  |

|           | 2.2.2 TMDL                                                 | 13 |  |  |

|           | 2.2.3 MDL                                                  | 15 |  |  |

|           | 2.2.4 Mop                                                  | 15 |  |  |

|           | 2.2.5 PO and VPO                                           | 16 |  |  |

|           | 2.2.6 The GNU C Compiler                                   | 18 |  |  |

|           | 2.2.7 Maril                                                | 19 |  |  |

| 2.3       | Multipurpose Descriptions                                  | 20 |  |  |

|           | 2.3.1 SLED                                                 | 20 |  |  |

|           | 2.3.2 λ-RTL                                                | 20 |  |  |

| 2.4       | Summary                                                    | 21 |  |  |

| Chapter 3 | — Specifying Instruction Semantics: CSDL Core Descriptions | 22 |  |  |

| 3.1       | String RTL's                                               | 23 |  |  |

|           | 3.1.1 String RTL Syntax and Semantics                      | 23 |  |  |

|           | 3.1.2 Analysis and Manipulation                            | 28 |  |  |

| 3.2       | τRTL's                                                     | 31 |  |  |

|        |       | .2.1     | Syntax                                   | 31 |

|--------|-------|----------|------------------------------------------|----|

|        |       | .2.2     | τRTL Types                               | 34 |

|        |       | .2.3     | Aliasing                                 | 36 |

|        | -     | .2.4     | Notation                                 | 38 |

|        |       | .2.5     | Abstract Syntax                          | 39 |

| 3.     |       | _        | tRTL's to Describe Machines              | 44 |

| 3.     |       | -        | ion Semantics – μRTL's                   | 47 |

| 3.     | .5 Si | umma     | ary                                      | 52 |

| Chapte | r 4 — | - Spec   | ifying Procedure Calling Conventions     | 54 |

| 4.     | .1 Ir | ntrodu   | ıction                                   | 54 |

|        | 4.    | .1.1     | Motivation                               | 55 |

|        | 4.    | .1.2     | Applications                             | 56 |

| 4.     | 2 P   | roced    | ure Calling Conventions                  | 57 |

|        | 4.    | .2.1     | A Simple Calling Convention              | 57 |

|        | 4.    | .2.2     | Convention, Language, and Implementation | 58 |

|        | 4.    | .2.3     | Separating Convention from Sequence      | 59 |

|        | 4.    | .2.4     | Interfaces and Agents                    | 60 |

|        | 4.    | .2.5     | Addressing                               | 61 |

|        | 4.    | .2.6     | Activation Frame Layout                  | 62 |

| 4.     | .3 T  | The CO   | CL Specification Language                | 62 |

|        | 4.    | .3.1     | Design Philosophy                        | 62 |

|        | 4.    | .3.2     | Resources                                | 63 |

|        | 4.    | .3.3     | Global Section                           | 64 |

|        | 4.    | .3.4     | Agent Descriptions                       | 65 |

|        | 4.    | .3.5     | Summary                                  | 70 |

| 4.     | 4 T   | he Fo    | rmal Model                               | 70 |

|        | 4.    | .4.1     | P-FSA Representation                     | 70 |

|        |       | .4.2     | Automatic P-FSA Construction             | 75 |

|        | 4.    | .4.3     | Completeness and Consistency in P-FSA's  | 77 |

| 4.     | .5 U  | Jse in a | a Compiler                               | 80 |

|        | 4.    | .5.1     | The Interpreter                          | 80 |

|        | 4.    | .5.2     | Realizing the Calling Sequence           | 81 |

| 4.     | .6 C  | Constri  | uction of Diagnostic Programs            | 85 |

|        | 4.    | .6.1     | Test Vector Selection                    | 85 |

|        | 4.    | .6.2     | Test Case Generation                     | 90 |

|        | 4.    | .6.3     | Automatic Diagnosis of Errors            | 92 |

|        | 4.    | .6.4     | Test Results                             | 95 |

| 4.     | .7 Si | umma     | ary                                      | 98 |

| Chapter 5  | — Computing System Description Language | 100     |

|------------|-----------------------------------------|---------|

| 5.1        | CSDL Overview                           | 101     |

|            |                                         | 102     |

|            |                                         | 103     |

|            | 5.1.3 Application Annotations           | 104     |

|            | • •                                     | 106     |

| 5.2        | •                                       | 107     |

|            | •                                       | 107     |

|            |                                         | 112     |

|            |                                         | 117     |

| 5.3        | · ·                                     | 118     |

|            | **                                      | 118     |

|            | •                                       | 120     |

| 5.4        |                                         | 121     |

| Chapter 6  | — Conclusions                           | 123     |

| Appendix A | A — CSDL Descriptions                   | 128     |

| A.1        | The MIPS Core Description               | 128     |

| A.2        |                                         | 133     |

| Appendix 1 | B — CCL Descriptions                    | 137     |

| 2.1        | The MIPS R3000 CCL Description          | 137     |

| 2.2        | 1                                       | 139     |

| 2.3        |                                         | 140     |

| 2.4        |                                         | <br>141 |

| 2.5        |                                         | 142     |

| Deferences |                                         | 111     |

#### **LIST OF FIGURES**

| Chapter 1 — Intro | oduction                                                                                |    |

|-------------------|-----------------------------------------------------------------------------------------|----|

| Figure 1-1.       | Procedural machines description use                                                     | 9  |

| Figure 1-2.       | Declarative machine description use                                                     | 4  |

| Ü                 | •                                                                                       |    |

| Chapter 2 — Con   | nputing System Descriptions                                                             |    |

| Chapter 3 — Spec  | cifying Instruction Semantics: CSDL Core Descriptions                                   |    |

| Figure 3-1.       | Context-free grammar for τRTL's                                                         | 34 |

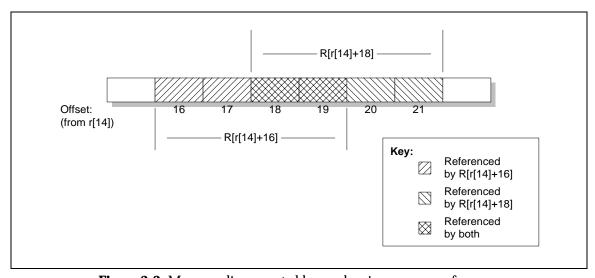

| Figure 3-2.       | Memory aliases created by overlapping memory references                                 | 37 |

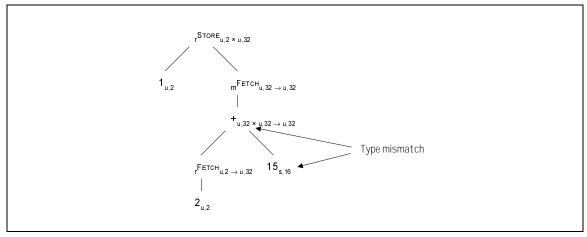

| Figure 3-3.       | Improperly typed τRTL for a load                                                        | 42 |

| Figure 3-4.       | A properly typed $\tau RTL$ for a load                                                  | 42 |

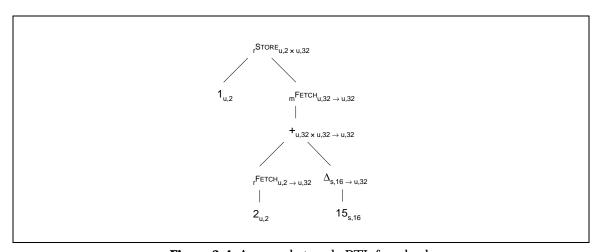

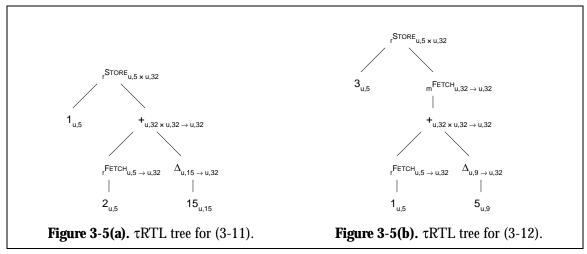

| Figure 3-5.       | Abstract syntax for two τRTL's                                                          | 43 |

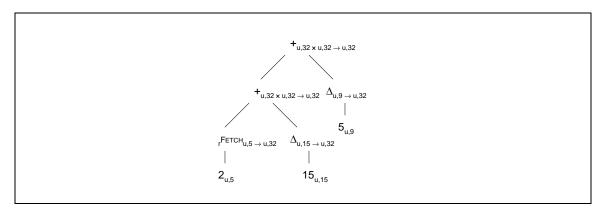

| Figure 3-6.       | Combined subexpression                                                                  | 43 |

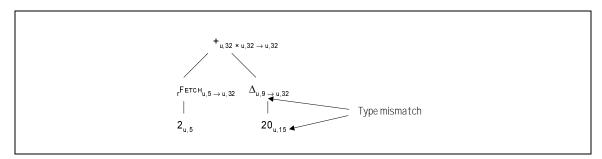

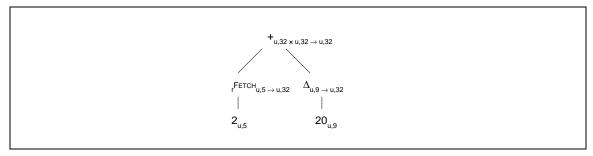

| Figure 3-7.       | Incorrect simplification of $(r[2_{u,5}]_{u,32} + \Delta(20_{u,9})_{u,32})_{u,32}$ tree | 43 |

| Figure 3-8.       | Correct simplification of $(r[2_{u,5}]_{u,32} + \Delta(20_{u,9})_{u,32})_{u,32}$ tree   | 4  |

| Figure 3-9.       | An τRTL grammar for a very simple machine                                               | 45 |

| Figure 3-10.      | An illegal $\tau$ RTL grammar                                                           | 4  |

| Figure 3-11.      | A properly formed τRTL grammar                                                          | 46 |

| Figure 3-12.      | A complete $\tau RTL$ machine description of the DLX                                    | 48 |

| Figure 3-13.      | µRTL operational semantics for a user-defined string copy operator                      | 5  |

| Figure 3-14.      | Operational semantics for the Pentium PADDB instruction                                 | 52 |

| Chapter 4 — Spec  | cifying Procedure Calling Conventions                                                   |    |

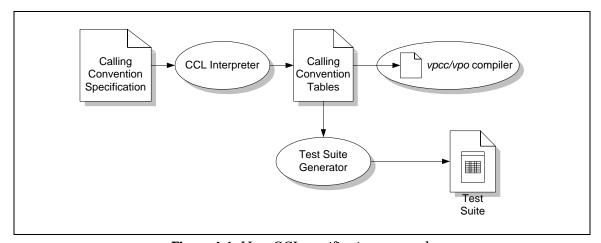

| Figure 4-1.       | How CCL specifications are used                                                         | 56 |

| Figure 4-2.       | Rules for a simple calling convention                                                   | 57 |

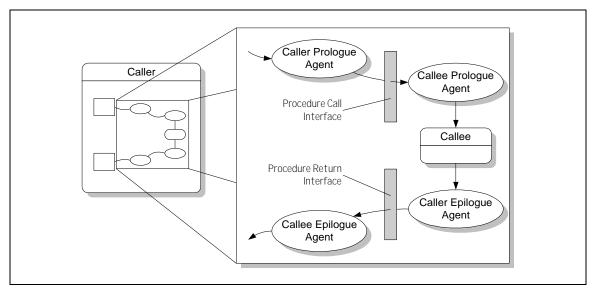

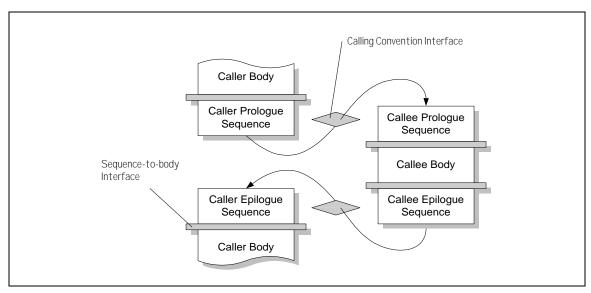

| Figure 4-3.       | The role of agents in procedure call and return interfaces                              | 6  |

| Figure 4-4.       | The caller prologue                                                                     | 68 |

| Figure 4-5.       | A CCL description of the calling convention of Figure 4-2                               | 7  |

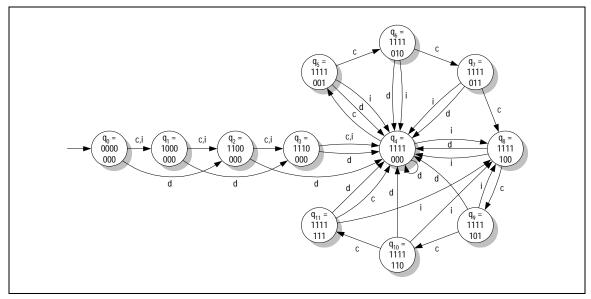

| Figure 4-6.       | P-FSA for transmission of parameters for a simple calling convention                    | 72 |

| Figure 4-7.       | Algorithm to build a P-FSA                                                              | 76 |

| Figure 4-8.     | Definition of State-Label                                   | 77  |

|-----------------|-------------------------------------------------------------|-----|

| Figure 4-9.     | Calling sequence locations                                  | 82  |

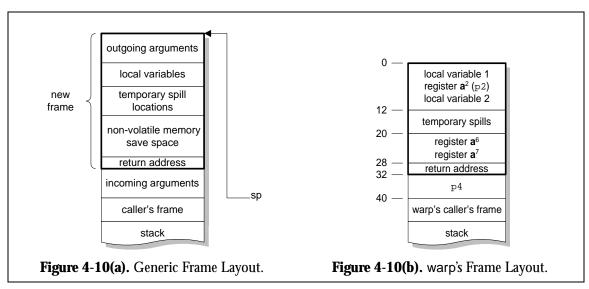

| Figure 4-10.    | A possible procedure activation frame structure             | 83  |

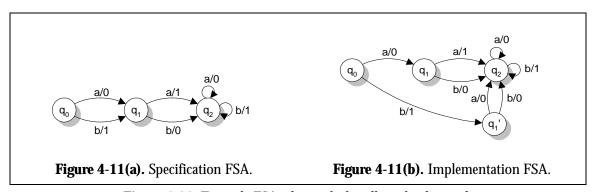

| Figure 4-11.    | Example FSA where a fault will not be detected              | 87  |

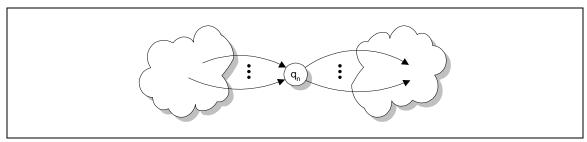

| Figure 4-12.    | Entering and exiting transitions for a state                | 88  |

| Figure 4-13.    | Test vector generation algorithm                            | 89  |

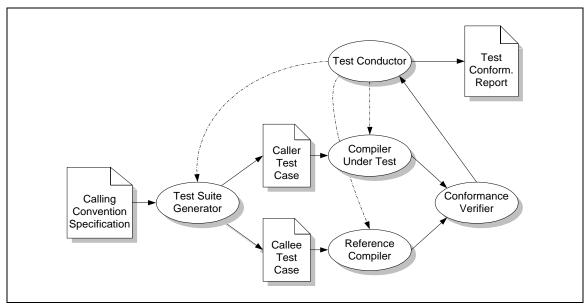

| Figure 4-14.    | The compiler conformance test process                       | 91  |

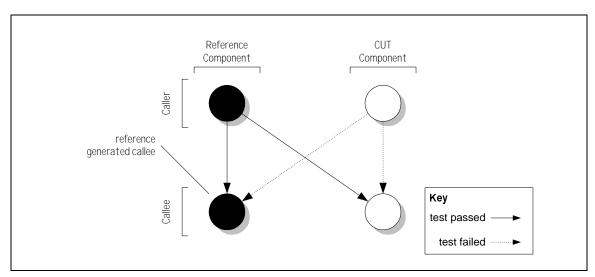

| Figure 4-15.    | An example outcome                                          | 92  |

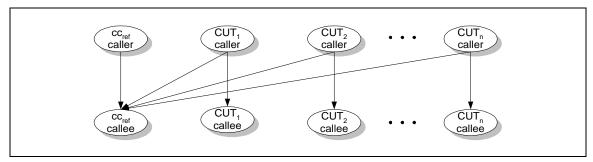

| Figure 4-16.    | Determining conformance of <i>n</i> compilers               | 96  |

|                 |                                                             |     |

| Chapter 5 — Com | nputing System Description Language                         |     |

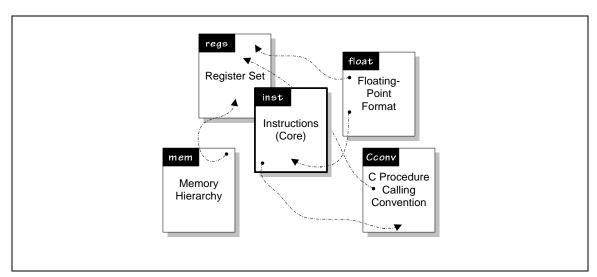

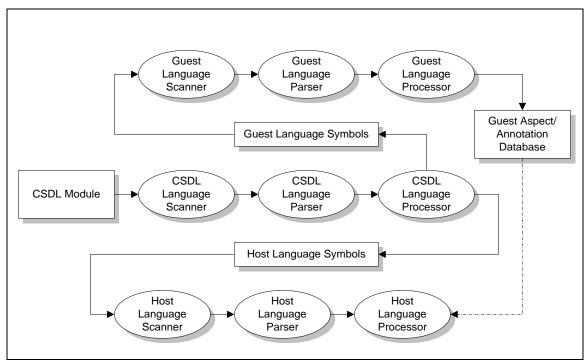

| Figure 5-1.     | Computing system description framework                      | 102 |

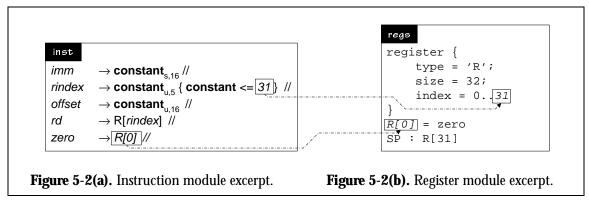

| Figure 5-2.     | Linked values                                               | 104 |

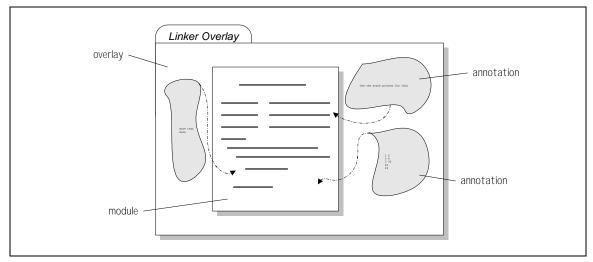

| Figure 5-3.     | An application's annotation overlay                         | 105 |

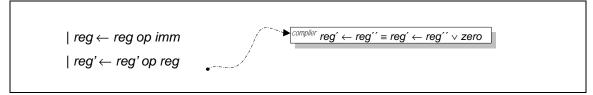

| Figure 5-4.     | A CSDL annotation                                           | 106 |

| Figure 5-5.     | Assembly language and binary format aspects of instructions | 107 |

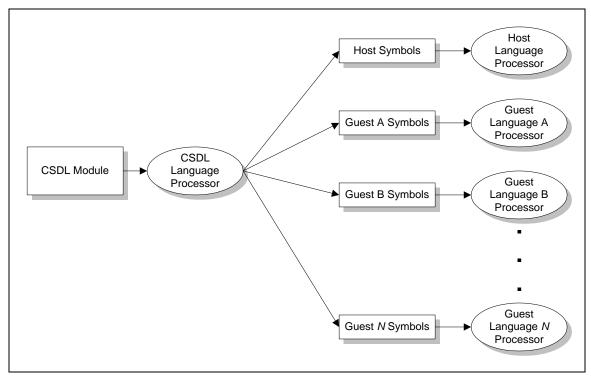

| Figure 5-6.     | CSDL Language Dispatching                                   | 108 |

| Figure 5-7.     | CSDL Grammar                                                | 108 |

| Figure 5-8.     | Processing of a CSDL module                                 | 110 |

| Figure 5-9.     | Specifying binary translation using a CSDL aspect           | 119 |

| Figure 5-10.    | A small MIPS excerpt with SLED aspects                      | 121 |

| Chapter 6 — Con | clusions                                                    |     |

| Appendix A — CS | DL Descriptions                                             |     |

| Appendix B — CC | CL Descriptions                                             |     |

#### **LIST OF TABLES**

| Chapter 1 — Inti | roduction                                                   |    |

|------------------|-------------------------------------------------------------|----|

| Chapter 2 — Coi  | mputing System Descriptions                                 |    |

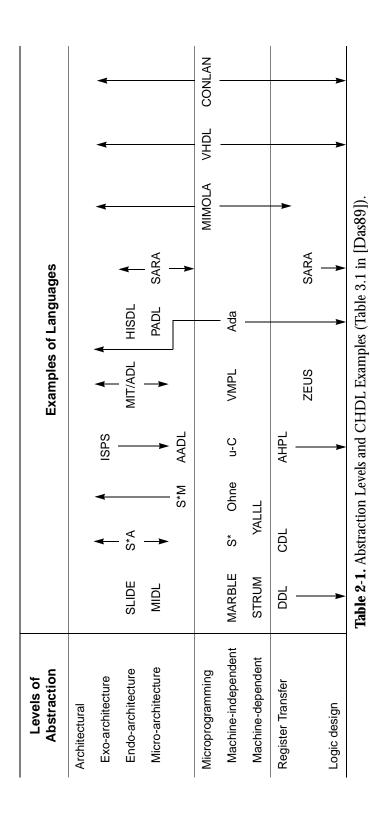

| Table 2-1.       | Abstraction Levels and CHDL Examples (Table 3.1 in [Das89]) | 10 |

| Chapter 3 — Spe  | cifying Instruction Semantics: CSDL Core Descriptions       |    |

| Table 3-1.       | Sample RTL address expressions (excerpted from [Ben94])     | 26 |

| Table 3-2.       | Summary of formats for string RTL expressions               | 27 |

| Table 3-3.       | Built-in RTL operator summary                               | 40 |

| Table 3-4.       | Summary of τRTL built-in operations                         | 50 |

| Chapter 4 — Spe  | cifying Procedure Calling Conventions                       |    |

| Table 4-1.       | Definition of $\lambda$ for example P-FSA                   | 75 |

| Table 4-2.       | Determining agent actions from placement information        | 84 |

| Table 4-3.       | P-FSA profiles for several calling conventions              | 86 |

| Table 4-4.       | Sizes of test suites for various selection methods          | 88 |

| Table 4-5.       | All outcome configurations                                  | 94 |

| Table 4-6.       | Results of running the MIPS test suite on several compilers | 96 |

| Chapter 5 — Co   | mputing System Description Language                         |    |

| Chapter 6 — Co   | nclusions                                                   |    |

| Appendix A — C   | SDL Descriptions                                            |    |

| Appendix B — C   | CL Descriptions                                             |    |

#### CHAPTER 1

#### INTRODUCTION

In an era of rapid design of microprocessors for desktop systems, embedded systems, and handheld computing devices, the timely construction of systems software is essential. Systems software, such as assemblers, compilers, and debuggers, must be constructed before development of application software for a microprocessor can commence. However, the implementation of such machine-specific applications is difficult and time consuming. Therefore, to remain competitive, it is imperative that systems software designs focus on portability to reduce implementation time and ensure rapid delivery of complete systems to the market.

A proven technique for building portable systems software—particularly compilers—is to isolate machine-specific details of an implementation through the use of a machine description. A *machine description* is the specification of a machine's features that the implementation needs to perform its task. The machine description is used to automatically generate the machine-specific portion of the application's implementation. In theory, the machine description focuses on describing the machine rather than describing the implementation. In practice, machine descriptions often describe not only the machine, but also the process by which the machine's features are used in the implementation. Such descriptions contain application dependencies that preclude their reuse in other applications. Unfortunately, description systems, and the machine descriptions they contain are, themselves, difficult and time consuming to construct. This research concentrates on the design of description languages that promote writing reusable computing system descriptions.

1

Chapter 1: Introduction Background

2

#### 1.1 Background

A survey of machine description techniques reveals two approaches to describing machines: the procedural approach and the declarative approach. The procedural approach uses an implementation to present the features of the target machine to the application. By interpreting the implementation, the desired machine-specific features are recognized. The second approach uses a table, or database, of information. Aspects of an application's implementation that are machine-specific are located in the table for convenient access by the application.

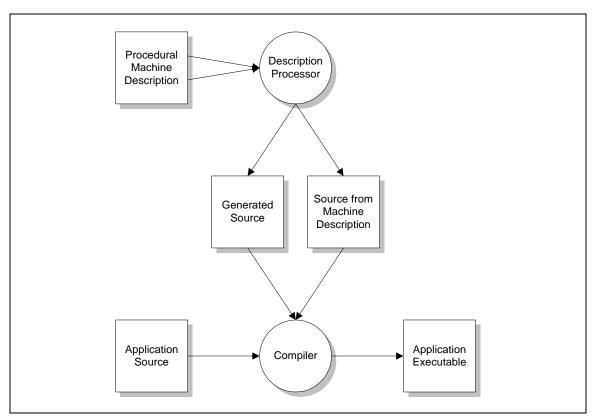

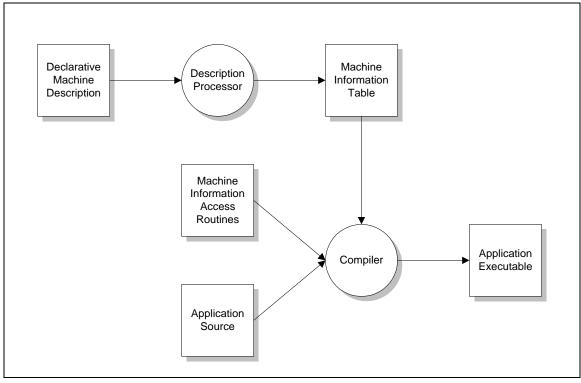

In the procedural approach, the machine description is read by a description processor which passes through source code taken from the machine description and, optionally, generates additional code from other parts of the description. Figure 1-1 depicts this process. This method has two advantages. Foremost, it is easy to implement. Often, the description is written in a special-purpose language that is augmented by the application's implementation language. Shortcomings in the special-purpose language can easily be addressed by using the application's implementation language. The other advantage to this approach is that the description language is extensible. If the application's implementation language is used, then all of the procedural and data abstraction facilities of the implementation language are available. This approach, however, also has its limitations. First, the machine descriptions are specific to an application. This makes them difficult to reuse, even though the information they contain could be useful to other applications. Second, while the characteristics of a target machine may be easy to understand, it is usually difficult for someone unfamiliar with the application's implementation to write a description of a new target machine. Third, since the descriptions are implementations, they suffer the problems of any implementation: they are difficult to read and maintain. Fourth, since these implementations are typically written in an *ad-hoc* manner, it is difficult to prove anything about the resulting descriptions.

In the declarative approach the machine description contains little or no source code. Instead, machine-independent source code that accesses the machine-dependent table is included in the application. The description processor then produces a table in the form of code that will be accessed by the supplied access routines. This process is shown in Figure 1-2. The declarative method is significantly better than the procedural technique. First, the descriptions have a fixed format. This makes them more straightforward. The details of the target machine are simply placed in the appropriate entries in the table. Thus, the descriptions

Chapter 1: Introduction Background

3

Figure 1-1. Procedural machines description use.

Figure 1-2. Declarative machine description use.

Chapter 1: Introduction The Problem

4

are more compact and concise. Consequently, they are easier to write, read and maintain. Second, a program can automatically generate, from the description tables, an implementation that is similar to the procedural approach in function and form. Also, the resulting implementation is likely to be more robust. Third, all descriptions have a similar form; similar characteristics are described in similar ways. Hence, applications using these descriptions are more easily retargeted. Fourth, this approach can be more application-independent. This approach has one disadvantage: it may be difficult to describe all of the relevant information about the target machine if the table is not general enough.

#### 1.2 The Problem

The use of a machine description can significantly reduce the time to retarget an application. However, with each retarget of the application, a description for the new target machine must be written. For an application of any substance, this itself can be a daunting task. There are three sources of difficulty:

- 1. Information about the machine must be found, encoded using whatever description technique is used, and it must be tested, verified, and debugged to ensure accuracy. For some machines, the finding of information is itself difficult. For some applications, the sheer volume of information to be encoded is a significant obstacle.

- 2. A description system that is tailored for a particular application usually contains bias toward that application. Thus, for example, a retargetable compilation system may include a machine description facility. This facility may require that information be encoded in a particular way, or that only some information be encoded. Typically, only an expert familiar with the compiler can write such a description though the concepts that are described do not require expertise in compilers to understand.

- 3. Because the application does not share a common description format with other applications, one can be certain that there is not already a description available for one's use.

Using a common description format that contains no application bias eliminates these three sources of difficulties. Such a description facility is called *application independent*. Obviously for an application independent description it may at least be possible that the description already exists for the new target machine (source 3). Further, no knowledge of a particular application is required to successfully write a description (source 2). Thus any computer pro-

Chapter 1: Introduction Motivation

5

fessional who is familiar with the machine should be qualified to write a description. Finally, if an application-independent description system becomes widely used, finding information about a target machine should become easier since computer manufacturers could supply documentation about the machine in the form of a system description (source 1).

The goal of this research is to develop a more effective method for describing target machines. For the method to be *effective*, it should be application independent. The class of machines we support is the traditional von Neumann architectures. The level of abstraction is the view that applications, such as assemblers, compilers and debuggers, have of the target machines.

#### 1.3 Motivation

Although there have been numerous efforts to design machine description techniques, many of which have been successful, none of these solutions have been very general, complete, or application-independent.

For many years, compilers have used machine descriptions to capture details about the compiler's target machine. Through the use of a machine description, target-specific information can be isolated from the rest of the implementation so that it may easily be examined and changed. Despite their success in compilers, machine descriptions have not been widely used by other systems software such as linkers, debuggers, profilers, and simulators. For the most part, where machine descriptions have been used, new systems have been developed rather borrowing the technology from an extant description system. A primary motive for this action is that machine descriptions have been *application dependent*. That is, inherent in the way the description is written is the purpose for which the application will use the information. This application dependence stifles the reuse of descriptions in other applications.

By providing a more complete description method, we can reduce the retarget time of applications. Current techniques manage only to describe a subset of the characteristics of the target machine. In doing so, these methods require that the remaining characteristics be provided in a less retargetable form.

In addition to completeness, we see the need for a more general solution. Many of the existing description systems only allow the description of a small class of machines—such as

Chapter 1: Introduction Structure

6

Reduced Instruction-Set Computers (RISC's). These systems, therefore, are of limited use to retargetable applications.

Current methods of description have been designed with a specific application in mind, despite the fact that the following applications can use information about the target machine at the same level of abstraction:

- Assemblers Assemblers require information about the instructions and data types of the target machine. They also require the binary format of each of the instructions.

- Compilers Compilers need instruction information (both binary and symbolic),

resource information (registers, functional units, busses, etc.), details of the subprogram calling convention, etc.

- **Debuggers** For disassembly purposes, debuggers need information about the binary format of instructions and their respective symbolic form.

- Emulators/Simulators These applications require information at the appropriate level

of abstraction. In this case, what instructions are available and their syntax and semantics.

- Synthesis tools Tools for synthesis require similar information as simulators.

- Evaluation tools For example, profilers require resource and instruction information.

- Testing tools Automatic testing and verification tools can use the instructions and resources as a basis for their testing.

- Documentation People could use a formal description as a form of machine documentation.

Thus, there is clearly a need for an application-independent description technique. With such a description facility, all of the above tools could use a single description. This, in fact, changes the role of the description language to that of a definition language. By standardizing the descriptions, we can establish a formal method of communication among computer architects and software developers.

#### 1.4 Structure

The following chapter presents a brief overview of previous machine description systems.

Chapter three presents the CSDL (Computing System Description Language) core language used to describe a machine's instruction set. Chapter four discusses the Calling Convention

Chapter 1: Introduction Structure

7

Language that we use to describe a machine's procedure calling convention. Chapter five presents the general CSDL framework that delivers flexibility and extensibility to the applications that use CSDL. Chapter six concludes by summarizing the research results and contributions of this work.

#### CHAPTER 2

#### **COMPUTING SYSTEM DESCRIPTIONS**

Since the 1960's researchers have investigated methods for effectively describing computing systems. Over the years, three categories of descriptions have emerged: computer hardware description languages, machine descriptions, and multipurpose descriptions. *Computer hardware description languages* (CHDL's) focus exclusively on the hardware for the purpose of simulation and synthesis of the hardware. *Machine descriptions* aim to isolate machine-specific characteristics of an implementation—typically a compiler—with the goal of making the implementation retargetable. Multipurpose descriptions aim to provide the same service as machine descriptions with the primary goal of serving a wider application audience. In this chapter, we present languages from each of these three categories in turn.

#### 2.1 Computer Hardware Description Languages

Hardware designers started developing and using languages for the description of computer hardware systems in the 1960's. These languages, called Computer Hardware Description Languages (CHDL's) represent the earliest attempts to describe machines.

An important characteristic of a CHDL is the level of abstraction that the language was intended to be used for. The level of abstraction refers to the logical level of computer design that the language most naturally describes. Examples of abstraction levels include register transfer, microprogramming and microarchitecture. Languages that are best suited for a particular design level, such as the register transfer, typically have a notion of objects native to the design level (*e.g.*, registers). The direct support of such objects in CHDL's give them their expressive power, and also limit their scope of applicability. The support of objects at a partic-

ular abstraction level makes descriptions at that level natural to read and write, while making the description at other levels, whose objects are not directly supported, awkward if even possible.

The plethora of CHDL's makes a thorough discussion of them here infeasible (Dasgupta presents a more in-depth discussion [Das89]). Table 2-1 (from [Das89]) presents examples of CHDL's representative of each of a number of levels of abstraction. Notice that a large number of these languages attempt, to some degree, to be multi-level. Since applications often view machines at a higher level of abstraction than most CHDL's are designed to present, the multi-level CHDL's appear to be the most promising candidates for building retargetable applications.

The abundance of CHDL's has given designers a large selection of description methods; it has also stifled language standardization. In an effort to alleviate the situation, the U.S. Department of Defense (DoD) has developed, as part of its Very High Speed Integrated Circuits (VHISC) project, a DoD standard CHDL called VHDL. As a result, VHDL is rapidly being adopted as an industry-wide standard CHDL. We will, therefore, review VHDL [Coe89, LSU89] which is representative of these multi-level languages.

#### 2.1.1 VHDL

A VHDL description is composed of *design entities* that are organized hierarchically. An entity, in turn, is composed of an *interface* and one or more *bodies*. An interface defines *ports* which are the only method of communication between an entity and other entities. There are two types of bodies: structural and behavioral. A structural body simply connects the entity's ports to ports of sub-entities contained in the entity body. A behavioral body, on the other hand, specifies the behavior of an entity using a procedural language. Behavioral bodies are used to define simple entities, while structural bodies are used to hierarchically build new composite entities from existing ones.

Data objects in VHDL may be one of constant, variable, or signal. Constants and variables are similar to their counterparts in programming languages. Signals, however, are new. A *signal* is connected to an interface port, and holds a value just as a variable does, but has an additional dimension—time. Signals are changed using a signal assignment. The assignment occurs when a value in the assignment (another signal) changes value. A time

delay may also be added to delay when the assignment takes place. Thus, signals may easily be used to model the wire connections of a computer.

In summary, VHDL uses entities to model the components of a system. Just as components are made up of sub-components, entities may be constructed using sub-entities. Wires connecting components are modeled using signals connecting ports. Finally, the behavior of the simple entities is described using a procedural language.

VHDL has a number of strengths. The hierarchical design makes it possible to manage descriptions of large, complex systems. Information about the behavior of components of the system can be precisely defined. Further, VHDL already has an established user base in simulation, design and synthesis, which could facilitate the sharing of descriptions. Unfortunately, for our purposes, VHDL's shortcomings are severe. The descriptions provide information at an inappropriate level of abstraction, making it difficult to extract the needed information.

#### 2.1.2 ISP

The first language to deviate from describing purely hardware is Bell and Newell's ISP (Instruction-set Processor) descriptive system [BN71]. However, we still place ISP in the CHDL category. ISP focuses on characteristics of the instruction-set architecture (ISA). The purpose of the notation is to uniformly describe instruction sets of a variety of machines. An ISP description has two parts: "the nature of the operations and the rules of interpretation." As such, Bell and Newell argue that this completely describes the behavior of the machine.

A typical ISP description is divided into five sections: the processor state, instruction format, effective address calculation, instruction interpretive process, and instruction set. The processor state and instruction format sections define the names and sizes of storage locations and instruction fields, respectively. The remaining three sections use a more procedural approach. Rather than describing what an instruction does, or what addressing modes are available, ISP descriptions describe how each of these work. Addressing modes are defined in terms of operations on the previously declared storage locations. Instructions are defined by their effect on the state of the machine using a register transfer notation to indicate the semantics. Finally, the instruction interpreter is defined in a similar way by using register transfers to describe the interpreter's effect on the state of the machine.

ISP has a couple of good points. First, it is general. This is illustrated by the *forty* machine descriptions provided in Bell and Newell's book. Second, the entire "programmer's view" of the system, as defined by the programmer's manual, can be described. Third, the language provides detailed information about the binary format of the machine's instructions. This is very useful information for applications that manipulate machine code.

Bell and Newell's system has several serious disadvantages, though. First, ISP describes machines at the wrong level of abstraction. Graham notes that "ISP contained **too much** detail, making it hard to extract the needed information from the description" [GH84]. Second, the descriptive system provides no information about software conventions, which are of interest to our applications. Third, ISP is not formal; its syntax and semantics are open-ended which makes it unusable by an automated system [Lun83]. This is primarily because ISP was designed as a notation for communicating machine characteristics between people [Wic75]. Thus, for an automated system to use ISP, a number of restrictions would have to be imposed on the language.

#### **2.1.3 LISAS**

Cook and Harcourt also describe the instruction-set architecture using a specification language called LISAS [Coo94, CH94a, CH94b]. LISAS is described as a functional language that models machines as a machine state and transformations on that state. The descriptions include storage bases, access classes (instead of operand addressing), data type descriptions, and instruction formats. Cook aims for application independence and raising the level of abstraction above CHDL's.

Unlike the other description systems, LISAS was designed for instruction-set simulation. This places them squarely in the class of CHDL's. A LISAS description presents information at a level of abstraction somewhere between CHDL's and machine descriptions. Although Cook claims that LISAS can be used for applications other than simulation, it is not at all apparent how applications that generate assembly language could make use of the descriptions since they detail the binary format of instructions, but not the symbolic assembly format. LISAS primary abstraction seems to be the instruction. If one wishes to describe other architectural features, such as the instruction execution pipeline, it is not clear how one could accomplish this within the current LISAS framework.

#### 2.2 Machine Descriptions

Unlike traditional CHDL's, Bell and Newell's ISP appealed to systems software developers. Shortly after ISP's introduction, machine descriptions emerged to aid in the construction of both assemblers and compilers. Machine descriptions are used to isolate and describe features of computing systems for retargetable software. In this section, present the most successful machine description systems.

#### 2.2.1 ISP'

Despite its shortcomings, ISP forms a foundation for many subsequent description systems. Since ISP has never been formally defined, a number of interpretations have evolved. One such interpretation is Wick's ISP´ which is used in his assembler generating system [Wic75], and also in Fraser's automatic code-generator generator [Fra77a, Fra77b]. ISP´ has a formal definition for its syntax and semantics, thus enabling it to be parsed, and used by such systems. Wick's system, however, places very few demands on the machine description system. In particular, the assembler generator has no need for a description of the semantics of each instruction, although they are present. Only details such as the binary format of the instructions, their mnemonics, and the data type encodings are used [Fra77b].

#### 2.2.2 TMDL

One of the first to abandon the ISP notation were Graham and Glanville. They use a machine description to enhance the retargetability of their table-driven code generation system [GG78b, GG78a]. Their language, called TMDL (Target Machine Description Language), uses attribute-grammar productions as its form of machine description. A machine description is composed of sections that describe the resources of the machine (such as the register set) and the instruction set.

The resource description is rather limited; it allows for specification of "logical groupings of register classes and pairs," and of which registers are available for allocation. The instruction-set section, however, is much more flexible. Instructions are described using a syntax-directed translation [ASU86]. Each target machine instruction is "described" using a

<sup>1.</sup> Ganapathi and Fischer have subsequently used this technique in their description-driven code-generation system [GF82].

semantically equivalent intermediate representation (IR) expression and a template for the corresponding assembly language instruction. Code is generated for the target machine by finding an instruction in the table that matches the IR expression. The assembly language template provides the translation from the IR to the target machine's assembly language. So, TMDL is not a machine description, but instead a code generator description.

Early versions of TMDL required a separate rule for each combination of instruction and addressing mode. Graham and Henry refer to this structure as a "flat" grammar since every grammar rule corresponds to a single instruction. Thus, an instruction with three operands, each with four possible addressing modes would require  $4^3 = 64$  different rules! Complete descriptions of a machine like the VAX-11 [Dig78] would be impractically large, since it would require several million grammar rules [GH84]. Later versions "factored" the grammar allowing descriptions of common portions of instructions, such as addressing modes, to be centralized [GHS82].

TMDL, in its final form, is a significant improvement over previous languages. Since the descriptions are essentially syntax-directed translations, they are easy for the implementor (in this case, a compiler writer) to understand. The original goal of isolating the machine's instruction set and assembly language format has been accomplished. Consequently, a number of machines have been described, thus providing working compilers. Finally, this approach has, to some extent, managed to separate the implementation *using* the descriptions from the descriptions themselves. This feature diverges from the previous descriptions which are more procedural—making it more suitable for other applications.

TMDL has several shortcomings, however. Although the compiler implementation has been separated from the description, the description still reflects the purpose of the implementation. The choice of the intermediate language as a method for describing the semantics of instructions reduces the usefulness of TMDL as a description system for other applications. The language requires an understanding of the IR for the compiler system and of syntax-directed translation which are skills that should not be required to describe the characteristics of machines.

Eventually, Graham and Henry abandoned TMDL altogether. A new LISP-like description language, called LISPMD (LISP machine description), was created [AGH+84]. Although LISPMD's design evolved from TMDL, its syntax and semantics diverge from it.

LISPMD is much more a general pattern-processor than a description system. A description is composed of "meta-family patterns," "meta-rules," semantic actions, and cost and weighting factors for each instruction. The semantics and rules for macro expansion make writing, or even reading, machine descriptions daunting for someone unfamiliar with the implementation of the compiler, the description system, and LISP.

#### 2.2.3 MDL

Boulton and Goguen developed a machine description language (MDL) to aid in the development of retargetable compilers [BG79]. In particular, MDL was designed to describe instruction-sets and memory structures in a form that could be processed by a machine. MDL is a direct descendent of ISP. Consequently, they decompose their description into structures similar to ISP's. MDL has separate facilities for describing the instruction semantics, instruction format, the structure of memory and data, and basic units (the basic addressable unit, number base, and instruction alignment). MDL is also hierarchical; basic units such as memory structure are used to describe the instruction format, which is subsequently used in the instruction description.

MDL provides a great deal of information at the bottom of its hierarchical structure. Details such as the base of the number system used by the machine and the data representation encoding (two's-complement, sign-magnitude, EBCDIC, etc.) are easily expressed. In addition, structures with similar properties can be grouped together, resulting in a more compact description. However, higher in the hierarchical description, where the language more closely interfaces with the intermediate language, details become more ad-hoc. In particular, unlike TMDL, the addressing modes for instructions are not separated from the form of the instructions. There is also no uniform model or formal language for the semantics of the instructions. Moreover, the addressing mode is implicitly derived from the format of the instructions. This greatly restricts the variety of instructions that can be described by the model.

#### 2.2.4 Mop

Cattell designed an instruction-set formalism for use in a machine-independent code generator for the PQCC (Production-Quality Compiler-Compiler) project at Carnegie Mellon University [LCH+80]. Cattell uses a declarative, rather than a procedural description called Mop

[Cat78, Cat80]. The model assumes, as ISP does, a machine composed of a processor and memory. Information provided by the model is divided into five categories:

- 1. *Storage bases*—locations that store the processor state. Each location is assigned a type, such as primary memory, reserved, or temporary.

- 2. *Operand addressing*—defined using an expression in terms of storage bases.

- 3. *Machine operations*—semantics of each instruction in terms of input and output assertions on the processor state. The semantics are described using a tree notation similar to the TMDL's. Attached to each instruction is its cost.

- 4. Data Types—size, type, and encoding of each supported data type.

- Instruction fields and formats—the format and encoding of each of the machine instructions described in the machine operations section. These also include the type and operand class of each instruction field.

As mentioned earlier, Mop is used with a machine-independent code generator. Cattell identifies problems in the interface between the description and the code generator. Specifically, he discovered that a set of general axioms were required to transform some intermediate language forms into different, equivalent forms that would match the semantic descriptions of the machine operations. The axioms are used to express the identity and commutativity relations for the operators in the intermediate language.

Many of the problems with TMDL descriptions can be found in Mop descriptions as well, since the semantic descriptions of instructions are similar to TMDL's. However, Cattell addressed several problems found in earlier systems. In particular, he determined that specifying the commutativity of operators should be solved *outside* the description of the target machine, in this case by using axioms. Cattell also observed that: "the machine representation does *not* say how to generate code for the machine in any way" [Cat80].

#### 2.2.5 PO and VPO

Davidson and Fraser use a machine description to achieve machine-independence in their peephole optimizer, PO [DF80, DF84b]. PO's descriptions use a technique similar to TDML. Consequently, the descriptions take the form of a grammar for syntax-directed translation. One significant difference is that Davidson and Fraser describe the effects of each instruction using ISP-like register transfers, called RTL's (Register Transfer Lists) [DF84b].

Although PO's notation allows storage locations to be named, the only name that has specific meaning is PC, which is used for the program counter. PO assumes that the PC will be incremented after each instruction, therefore, this effect need not be described by each instruction. Davidson makes an observation about the nature of machine descriptions at any level [DF80]:

"Details irrelevant to the object code may be omitted from the machine description.

... PO does not need to know how the condition code represents comparisons, so the machine description does not say."

Therefore, there are specific details about the machine, such as the condition code representation, that do not affect the interface to the machine. PO's machine descriptions are small; they can be written in an hour or two by someone familiar with the target machine.

Later, Davidson and Fraser developed a compiler—that used PO—for the Y programming language [DF84a]. Combiner<sup>1</sup>, a phase of PO, is retargeted using a machine description. However, Combiner does not use the description directly. Instead, the description is translated into a table that Combiner uses. Machine descriptions sometimes require tuning for the compiler to generate good code. Thus, Combiner is not tuned from machine to machine, making it more portable. Combiner does not make time-space trade-offs, so this information is not explicitly encoded in the machine description. Rather, the order of instructions is important in the descriptions. Thus, more specific instructions are placed before their more general, more expensive counterparts. In addition, PO uses a register assignment module that contains tables of information about the register set—a form of register description [DF84a].

Benitez and Davidson have since developed a successor to PO, called *vpo* [BD88, Ben89]. *vpo* uses an improved machine description technique. Many of the problems that Davidson discovered while using PO descriptions have been addressed. Both PO and *vpo* use the machine descriptions to generate recognizers for RTL's [Dav85]. PO descriptions were used to produce finite state automata (FSA) that recognized valid RTL's. Benitez and Davidson refined this method by using Yacc [Joh83] to generate the RTL recognizers [Dav85]. By

<sup>1.</sup> Combiner is the phase of PO that replaces sequences of register transfer instructions with single instructions that are semantically equivalent [DF84a].

using Yacc-based descriptions, they describe machines with large instruction sets more completely. Furthermore, the PO regular expressions used to generate the FSA's were not powerful enough to describe the assembly language expressions.

In addition to the Yacc-based description, *vpo* uses a formal description of register sets. Register sets are assigned type, size and alignment requirements. Furthermore, the register descriptions allow multiple abstract register sets to be mapped onto the same hardware register set. This provides multiple views of a single register set, which is convenient for machines that use the same registers to store floating-point and fixed-point values.

The *vpo* machine descriptions integrate the techniques used in ISP and PO. From PO, *vpo* takes its Yacc-based description. By using a grammar, common features can be factored and described in a single location. Also, since the description is a Yacc grammar, semantic actions can be used, providing additional flexibility. From ISP, *vpo* takes the register transfer notation (the RTL's) to describe the semantics of instructions. In fact, *vpo* uses RTL's to represent instructions throughout its optimization phases. The notation is a simple, intuitive, application-independent representation of instruction semantics.

Despite the benefits described above, *vpo* descriptions have a number of disadvantages. First, the LALR [ASU86] parsers generated by Yacc are still too restrictive. For some machines, it is difficult to remove reduce-reduce conflicts without compromising the conciseness or readability of the descriptions. Second, the addition of semantic actions, which at first seems beneficial, makes the descriptions more difficult to read since the information is distributed across multiple files. Third, *vpo* provides no formal description of software conventions. Finally, most of the description is still in the form of an implementation—making it less suitable for other applications.

#### 2.2.6 The GNU C Compiler

Using the ideas from PO, The Free Software Foundation's GNU C compiler [Sta92] also uses both RTL's and a machine description to attain retargetability. The machine description is broken into two parts: a set of instruction patterns, and a set of C macro definitions. The macro definitions parameterize the implementation by providing information about the target machine, such as storage layout (*e.g.*, big-endian or little-endian), sizes of supported data types, register usage, and subprogram calling convention. The instruction patterns contain

RTL templates, constraints on the missing pieces of the templates, and an output pattern or C code to generate the assembler output.

The GNU C compiler's machine description is probably the most thorough attempt at parameterizing an implementation. Most aspects of the target machine can be described, in some way, using the instruction patterns and macro definitions. The macro definitions isolate machine-specific details, but do not really *describe* the target architecture in any traditional sense. The technique is not only application-specific, but compiler-specific. Similar to PO, GNU's instruction patterns are used for peephole optimization. Unlike PO, these patterns use a combination of a complex LISP-like syntax for describing the RTL templates, and C code for specifying the format of the assembly output. This combination makes the patterns confusing and difficult to read. It would not be possible to reuse these descriptions since they are so tightly coupled with the implementation of the compiler.

#### 2.2.7 Maril

Bradlee, Henry and Eggers' Marian system [Bra91, BHE91] uses Maril, a machine description language, for describing not only the instruction set, but also the instruction scheduling properties and a limited register description. Maril is the first description system to incorporate details about instruction pipelines. Specifically, associated with each machine instruction are the resources, such as the fetch, decode and execution units, that the instruction requires during each cycle of its execution. This information makes it possible for Marion to use a machine-independent instruction-scheduling algorithm. Additionally, limited information about the register sets can be specified. This includes which registers are volatile or used to pass arguments, which registers are assigned to the frame and stack pointers, which registers hold the return address and return value, and registers that have constant value (e.g., a value of zero).

The Marian system is limited in its use of the description provided by Maril. For example, Marian uses *lcc* [FH91, FH95] to generate code. Since *lcc* has its own code generator, the description is not consulted during code generation; the only portion from the instruction description that is used is the pipeline resource information. Furthermore, it is not clear how effectively Marian uses the information it is given since none of the code generated by the compiler has been run on the target machines.

#### 2.3 Multipurpose Descriptions

As machine descriptions matured, three facts became apparent: 1) machine description systems are difficult to build, 2) machine descriptions are difficult to write and debug, and 3) machine descriptions contain information of interest to all sorts of retargetable applications. As a result, there has been a growing interest in machine description systems that can be used in more than a single application. In this section, we present languages that have the potential of being multipurpose descriptions.

#### 2.3.1 SLED

Ramsey and Fernandéz's New Jersey Machine Code Toolkit [RF95, RF97] aids in the development of programs that process machine code. The toolkit uses a Specification Language for Encoding and Decoding (SLED) machine code instructions. The toolkit presents the users with an assembly language level of abstraction. Tools that use the toolkit can easily read or emit machine code instructions through a procedural interface.

SLED descriptions concisely specify the binary format of a machine's instructions. From these descriptions, two different procedural interfaces can be generated: an interface that reads machine code and an interface that emits machine code. Using these interfaces, applications can be written that manipulate machine code in a machine-independent manner. The descriptions do not specify how the machine code will be manipulated, but rather the format of machine code.

SLED is a superb example of a description language that can be used for multiple purposes. Although SLED does not describe any other features of machine instructions—including their semantics—SLED provides an effective solution to a difficult problem: describing machine instruction formats. SLED would be a good choice for solving the encoding/decoding problem in a larger system.

#### 2.3.2 λ-RTL

The Zephyr component [ADR98] of DARPA and NSF's National Compiler Infrastructure includes  $\lambda$ -RTL machine descriptions developed by Ramsey and Davidson [RD98a, RD98b]. Since Zephyr uses vpo as its optimizer, it must model machine instructions as RTL's. Ramsey and Davidson attempt to formalize vpo's RTL's by using a description language called  $\lambda$ -RTL.

21

$\lambda$ -RTL is based on  $\lambda$ -calculus and models a machine's instructions as transformations on the machine's state.

The  $\lambda$ -RTL specification language is still being developed. However, initial descriptions yield insight into the nature of the language.  $\lambda$ -RTL imposes strong types on RTL's. However, because of the underlying formalism, often the  $\lambda$ -RTL processor can infer the types of operations without having to specify them everywhere. This makes the descriptions more compact, while, at the same time difficult to understand without reading the entire description. At this early stage, the effectiveness of  $\lambda$ -RTL has not been evaluated. Unfortunately, the specifications trade readability for conciseness to such a degree that it is not clear that anyone but the specification's author will be able to read them.

#### 2.4 Summary

This chapter presented examples of computer hardware description languages, machine descriptions, and potential multipurpose languages. CHDL's are used in the simulation and synthesis of hardware, while machine descriptions are used in the construction of software. In contrast to their predecessors, multipurpose descriptions attempt to separate what is being described from the description's use.

Although research in the field of computer description systems has been active, no system provides a complete or general solution to the problem. This body of work presents strong evidence that subsequent description systems should address the following problems:

- Retargetable software is difficult to write; so are machine description systems. New description systems should separate a description's form from its purpose.

- It is difficult to anticipate all the information that all applications may deem necessary.

Description systems should be extensible.

- Descriptions must not only be written, but read. Notation must be familiar to potential authors.

- Descriptions never seem to be complete. Incomplete descriptions should be usable.

- Different applications view machines differently. Descriptions must support multiple levels of abstraction and multiple views of a single abstraction.

#### CHAPTER 3

### SPECIFYING INSTRUCTION SEMANTICS: CSDL CORE DESCRIPTIONS

In the next three chapters, we develop a framework for building reusable computing system descriptions called CSDL (*Computing System Description Language*). We divide CSDL descriptions into components that are each responsible for describing one feature of a target architecture. In this chapter, we present the CSDL *core* component which is responsible for describing machine characteristics of interest to most, if not all, applications: the target architecture's instruction set.

A core description presents the instruction-set architecture of the machine. This abstraction level consists of the information that is necessary to produce or manipulate instructions for the target machine. We provide this information by defining the effects of instructions on the state of the machine.

Core descriptions are composed of two parts: the semantics of the instruction set and alternative forms or views of instructions such as the assembly language format, the binary encoding of instructions, or the cycle cost of instruction execution. In this chapter, we focus on the formal description of instruction semantics in isolation. Chapter 5 will present how core descriptions may be augmented with whatever additional information an application writer considers necessary.

Our instruction semantics are based on a register transfer notation called register transfer lists (RTL's), so we first present an extant register transfer notation.

#### 3.1 String RTL's

Traditional systems software generates, or operates on, assembly language or binary machine language instructions. Unfortunately, both of these forms of machine instructions vary from machine to machine. For example, to perform a 32-bit signed addition on the MIPS [KH92], the assembly language instruction is:

while on the Motorola 68020 [Mot85] the assembly form is:

these two instructions differ not in their semantics, but rather in their concrete syntax. One reason this difference occurs is that each assembler defines the format of lexical tokens (e.g., opcode mnemonics, registers, constants, and addressing modes) and the ways in which they may be combined (the assembly language). The result is that it is impossible to determine without knowing the particular assembly language whether the instruction:

adds registers two and three and places the result in register one, or if it adds registers three and one and stores the result in register two.

Such trivial machine dependencies, as well as far less trivial differences, can be eliminated by expressing the semantics of instructions using register transfers, or RTL's (Register Transfer Lists). One dialect of register transfers that is representative of the technique was developed by Davidson and Benitez [BD88]. This form, which we call "string RTL's," is presented in this section. RTL's make it possible for software to eliminate trivial syntactic differences and concentrate on semantic differences that reflect each machine's capabilities at the machine instruction level.

A highly successful method of eliminating machine dependencies is to express each machine instruction in a language whose semantics are invariant across platforms. Instructions are then manipulated in this language by systems software whose algorithms are machine independent.

#### 3.1.1 String RTL Syntax and Semantics

String RTL's are composed of registers, memory references, constants, labels, local and global identifiers, macros, and operators. We briefly describe the syntax of each of these tokens here.

#### 3.1.1.1 Registers

Registers are represented using the notation:

where r is a lower-case letter that indicates the type of value the register currently holds. num is a decimal number that indicates which register is being referenced. For example, b[5] typically designates the sixth register. This register holds a byte (thus, the b register type).

#### 3.1.1.2 Constants

Constants are always positive and can be either integer or floating-point. Integer constants are strings of decimal digits. Floating-point constants use the notation:

```

mantissa E sign exponent

```

where mantissa is a string of decimal digits representing the integer value of the mantissa, exponent is a string of decimal digits representing the value of the exponent, and sign is either '+' or '-' to indicate the sign of the exponent. Negative constants can be obtained by applying the unary negation operator ('-') to the constant.

#### 3.1.1.3 Operations

Register transfers not only transfer data from one location to another, they also perform various arithmetic and logical operations. The set of operations is limited to 36 built-in unary and binary operators that are available on most architectures. This includes the standard arithmetic operations such as addition and subtraction of signed integers (denoted '+' and '-', respectively), bitwise logical operations such as AND, OR, and NOT ('&', '|', and ' $\sim$ '), and relational operations such as less than, greater than, and equal ('<', '>', and ':'). Finally, an RTL effect is not complete without the assignment operator (':') which performs a store operation (thus the use of ':' for relational equal). The RTL effect:

$$r[1]=r[2]+r[3];$$

(3-1)

denotes that register two is added (using signed integer arithmetic) to register three with the result being placed in register one. The semicolon (';') marks the end of the effect. RTL operators are often overloaded, and the type of operation is determined by the type of the operands. For example, addition of two registers that contain floating-point values could be described using the effect:

Thus, the same operator, '+', is used to designate two different operations: signed-integer addition and floating-point addition.

#### 3.1.1.4 Macros

Often times, it is necessary to extend the set of built-in operations. This is accomplished using RTL function macros. A function macro is represented by an identifier composed of exactly two uppercase letters followed by a comma-separated list of expressions enclosed in brackets. A common use of function macros is to perform type conversions. For example, to convert a floating-point value into an integer value, one could introduce the FI macro:

```

r[5]=FI[f[5]];

```

The meaning of function macros is machine-dependent and is thus undefined by the notation. Their meaning must be implicitly understood by the algorithms that manipulate them.

Function macros are also used to abstract away the details of complex instructions. For example, the SAVE instruction on the SPARC [Sun87] that provides a new register window is described using the SV function macro:

```

r[14]=SV[r[14]+64];

```

This effect only indicates that r[14] is both read and written. The details of which registers are saved, and which registers change values because the register window has moved, remain unspecified.

In addition to function macros, string RTL's also allow for macros to be used to describe special storage locations in the target machine. Examples of these include PC and CC which designate the program counter and condition codes respectively.

#### 3.1.1.5 Memory

Memory references are represented using the notation:

```

M[address]

```

where M is an uppercase letter that indicates the type of value the memory location currently holds. address is an arbitrary RTL expression that indicates the address of the memory location being referenced. The RTL expression for a memory fetch using register displacement is:

In this case, the result of this expression is likely a single-precision floating-point value<sup>1</sup>. Unlike register indices, memory addresses may use arbitrarily complex expressions to represent the necessary addressing mode. Table 3-1 shows several of the most commonly known addressing modes.

| RTL Expression   | Addressing Mode     |

|------------------|---------------------|

| R[_global_id]    | memory direct       |

| R[w[4]]          | register indirect   |

| R[w[4]+12]       | displacement        |

| R[w[4]*4]        | scaled              |

| R[(w[4]*4)+12]   | scaled displacement |

| R[w[4]+w[7]]     | indexed             |

| R[R[_global_id]] | memory indirect     |

**Table 3-1.** Sample RTL address expressions (excerpted from [Ben94]).

## 3.1.1.6 Symbolic Addresses

String RTL's use three types of expressions to name memory addresses and constants symbolically. They are: labels, global identifiers, and local identifiers. Labels most commonly mark the target of a branch instruction. Labels are designated using the character 'L' followed by a decimal number (e.g., L15). Global identifiers mark constant address values and function entry points. A global is represented using a string of letters and digits (e.g., index0). Local identifiers usually represent constant offset values (typically from the stack pointer). A local is represented using a string of letters and digits followed by a period (e.g., i.).

Locals and globals, as well as other tokens, have an encoded string variation as their internal representation. The internal form uses two bytes to compactly store which symbol is referenced in the RTL. These two bytes are used as the key for a symbol table to quickly access all necessary symbol information, such as a symbol's offset.

#### 3.1.1.7 Instruction Effects

Ultimately, the purpose of string RTL's is to describe the effect a machine instruction has on the state of the target machine. This is achieved by combining the various string RTL expres-

<sup>1.</sup> Although there are conventions regarding the meaning of memory types, their meanings are machine dependent.

sions described above (and summarized in Table 3-2) into a list of instruction effects. An effect contains a single assignment operation on some storage location. In many cases, as shown above, instructions can be described using a single effect. Instructions that modify more than a single location are described using multiple string RTL effects. For example, on many machines, addition also sets a condition code register. This would be expressed using:

where the assignment to the macro CC describes the instruction's effect on the machine's condition codes. All expressions are assumed to be evaluated before any assignments are made.

| Туре                    | Regular Expression <sup>a</sup>                         | Example             |

|-------------------------|---------------------------------------------------------|---------------------|

| Register                | [a-z][[0-9] <sup>+</sup> ]                              | r[5]                |

| Integer Constant        | [0-9]+                                                  | 15                  |

| Floating-point Constant | [0-9]* <b>E</b> [+-][0-9]*                              | 15E10               |

| Operation               | expr <sup>b</sup> op <sup>c</sup> expr<br>or<br>op expr | r[1]+5              |

| Macro                   | [A-Z][A-Z]                                              | PC                  |

| Function Macro          | [A-Z][A-Z][ expr,]                                      | FI[f[5]]            |

| Memory Reference        | [A-Z][expr]                                             | R[r[14]+12]         |

| Local identifiers       | [A-Za-z0-9_]+•                                          | i.                  |

| Labels                  | <b>L</b> [0-9] <sup>+</sup>                             | L15                 |

| Global identifiers      | [A-Za-z0-9_]+                                           | _main               |

| effect                  | expr = expr;                                            | r[5]=12;            |

| RTL                     | effect+                                                 | r[1]=r[2];r[1]=r[2] |

**Table 3-2.** Summary of formats for string RTL expressions.

- a. Tokens are described using extended regular expressions. Literals are displayed in bold.

- b. *expr* is any RTL expression defined in the table.

- c. op is any one character RTL operator such as +, -, \*, /, <, >, etc.

#### 3.1.1.8 Transfers of Control

Instructions that perform transfers of control use several different formulations. Both conditional and unconditional branches are described by assigning to the program counter. The string RTL:

describes an unconditional branch to the instruction labeled L43. Conditional branches use the relational operators to compute the target address:

In this case, the PC is set to L43 only if the value of the condition codes equals zero. Otherwise, PC is not set by this effect. The list operator (',') is used to augment the assignment operator to designate conditional assignment.

The two other common forms of transfer of control are procedure call and return. Procedure calls are represented by assignment to the ST macro:

and returns are described as: